Đối với mỗi hệ thống pin năng lượng mặt trời, các module pin quang điện thường được xem là phần quan trọng nhất, chúng được đặt ở ngoài trời để hấp thụ ánh sáng và chuyển thành điện năng. Do vậy mà độ bền ở điều kiện ngoài trời của những sản phẩm này là một chỉ số chất lượng quan trọng, trong đó, hệ số LID – hệ số suy giảm cảm ứng ánh sáng là một trong những chỉ số thường được các chuyên gia, các hãng sản xuất và các đơn vị lắp đặt đem ra đề cập và so sánh nhiều nhất.

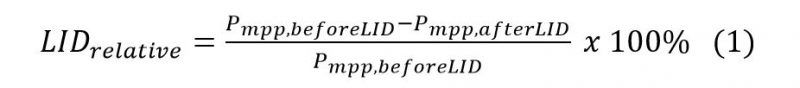

Về công thức toán học, LID trong các sản phẩm pin silicon mono và pin poly được định nghĩa như sau:

Việc đo lường đường cong tuyến tính I-V của các module pin trước và sau LID là cần thiết. Độ chính xác của phép đo I-V bị ảnh hưởng bởi nhiệt độ môi trường, sự điều chỉnh của lượng quang phổ mặt trời, v.v. Thông thường, mẫu tham chiếu sẽ được hiệu chuẩn bởi cơ quan thứ 3 có thẩm quyền chứng nhận để tạo mẫu tham chiếu thứ cấp. Ví dụ đối với hiệu chuẩn I-V bởi trình mô phỏng hiệu suất tấm năng lượng mặt trời hạng AAA tại TUV Rheinland, độ lặp lại là ± 0.1% và độ tái lập là ± 0.5%. Đối với các hãng sản xuất module pin, nếu không có chứng nhận hiệu chuẩn bởi cơ quan thứ 3 có thẩm quyền, độ không đảm bảo đo sẽ được tăng lên đến ± 2% do không khớp quang phổ.

Việc đo lường chính xác đường cong tuyến tính I-V của các tấm pin là điều kiện tiên quyết để so sánh LID.

LID theo nghĩa hẹp thường đề cập đến phức hợp broton – oxygen (hay còn gọi là BO-LID) gây ra bởi hàm lượng oxy có trong silicon nóng chảy trong quá trình Czochralski để thu được tinh thể silicon. BO-LID thường được coi là yếu tố chính ban đầu gây nên hiện tượng LID trong các tấm pin silicon đơn tinh thể hoặc đa tinh thể, và thường được phát hiện trong các tế cell pin được làm từ Silicon Cz pha tạp loại p. Theo tiêu chuẩn IEC 61215, hiện tượng tiền LID được tính toán bằng các phép đo I-V cho tấm pin trước và sau khi phơi sáng 5kwh.

Có 3 loại LID chính là: BO-LID (với nguồn gốc từ Broton-oxy), suy thoái do nhiệt độ cao và cường độ ánh sáng tăng – LeTID và UVID do sau khi tiếp xúc với tia cực tím. Bài viết này sẽ tập trung ở 2 dạng LID đầu tiên

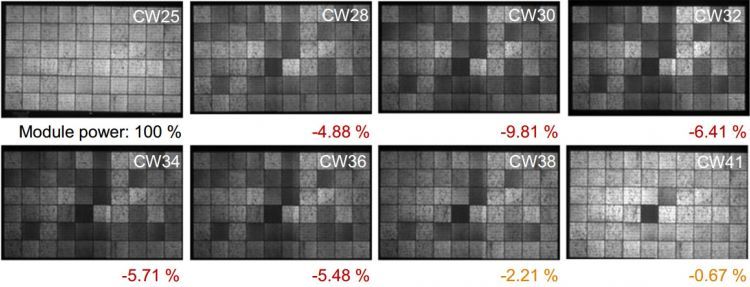

Vào năm 2015, Friederike Kersten và các cộng sự đã xuất bản trong cuốn Solar Energy Material & Solar Cells có nêu một hiện tượng nổi bật là LID được phát hiện trên nhiều module PERC. Hiện tượng suy hao này xảy ra nhiều hơn khi có nhiệt độ cao, và được gọi là sự suy hao do phơi sáng và dưới nhiệt độ cao (cụm từ nguyên bản là Light- and elevated Temperature-Induced Degradation, viết tắt là LeTID). Mặt sau của tấm pin thường được che phủ bằng xốp để duy trì hoạt động ở nhiệt độ cao. Sau 5 tuần (bảng pin mô phỏng số CW30), tấm module thí nghiệm đã đạt đến mức LeTID tối đa. Và những tấm module có hiện tượng LeTID chỉ có thể được phát hiện nếu đặt ở môi trường có nhiệt độ cao, trong đó, một số module poly trong các điều kiện thử nghiệm nhiệt độ cao đã suy hao đến 10% trên công suất tương ứng.

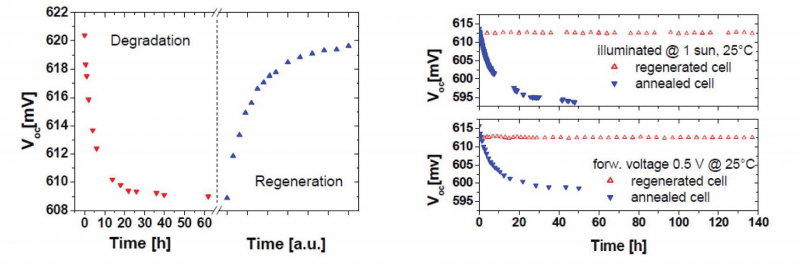

Với sự trợ giúp từ các vật liệu cách nhiệt, thí nghiệm đã chỉ ra được quá trình suy hao sau đó lại dần được cải thiện với chu kỳ là khoảng 4 tháng, được chỉ ra như hình 1 dưới đây:

Theo thông tin trên, phân tích dữ liệu LID bao gồm

- So sánh dữ liệu LID trên các thử nghiệm được lặp lại nhiều lần và có tính chính xác cao

- Khi nhiệt độ cell pin thấp, cơ chế LID được xác định ban đầu là BO-LID

- Khi nhiệt độ cell pin tương đối cao (ví dụ ở 75oC), hiện tượng LeTID bắt đầu xảy ra.

- LeTID mất một khoảng thời gian dài hơn để hiển thị do cơ chế vật lý của nó vẫn chưa rõ ràng

Hơn nữa, chất lượng của vật liệu silicon làm tấm pin, cấu trúc cell pin, cấu trúc module, vật liệu bảo vệ, đóng gói và điều kiện hoạt động tại môi trường lắp đặt đều ảnh hưởng đến kết quả LID, dẫn đến việc gia tăng sự phức tạp trong việc phát hiện nguyên nhân suy hao hiệu suất.

Sau khi hiểu được định nghĩa về BO-LID và LeTID, Long Tech sẽ giúp bạn tìm hiểu kỹ hơn về cơ chế và các khắc phục cho từng hiện tượng trên nhé:

Hiện tượng BO-LID

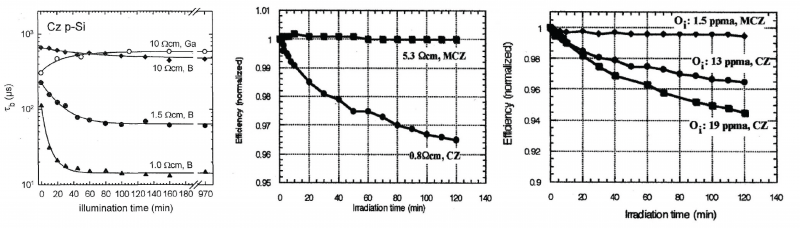

Cơ chế hình thành BO-LID và các phương pháp giải quyết vấn đề này đã được nghiên cứu từ trước những năm 2000. Vào năm 1997, Giáo sư Jan Schmidt từ ISFH đã tìm ra rằng sử dụng Ga như một nguồn pha tạp thay thế có thể giải quyết được hiện tượng BO-LID. Sau đó, Giáo sư T. Saitoh từ Đại học Nông nghiệp và Công nghệ Tokyo đã nghiên cứu về hiện tượng LID trên Ga pha tạp Cz, Boron pha tạp Cz, từ tính Cz và Fz như trong hình 2

Sự khác biệt của BO-LID giữa tấm pin Silicon đơn tinh thể (mono) và đa tinh thể (poly)

Trong các cells pin mà tấm wafer được làm từ loại P-type có pha tạp boron, BO-LID được xem là nguyên nhân chính cho các hiện tượng LID ban đầu.

Các tinh thể pin mono được hình thành trong quá trình nung silica bởi quá trình kéo phôi đòi hỏi phải nung chảy nguyên liệu này. Lớp phủ của nồi nấu kim loại không thể ngăn chặn hoàn toàn sự khuếch tán oxy từ phần vách của nồi nấu kim loại. Do vậy, lượng oxy hòa tan trong silicon nóng chảy bị tách ra thành từng khối riêng trong quá trình làm mát, dẫn đến nồng độ oxy trong các tế bào pin mono lên đến 10ppma.

So với quá trình nung và kéo phôi để tạo thành pin mono, thì pin poly lại có nhiều lợi thế hơn trong quá trình hình thành khuôn. Chúng bao gồm sự nóng chảy 1 phần của nguyên liệu Silica với lớp phủ SiNx hiệu quả của nồi nấu kim loại, diện tích bay hơi lớn hơn và diện tích tiếp xúc với nồi nấu kim loại nhỏ hơn.

Chính vì vậy, trong một mảnh vật liệu pin poly, chỉ có các vùng rìa gần với vách nồi nung kim loại có nồng độ oxy cao (khoảng 10ppma) trong khi ở khu vực trung tâm thì chỉ khoảng 1ppma. Và do diện tích nồi nấu là khá lớn, do vậy hàm lượng oxy trung bình trong dòng pin poly chỉ bằng khoảng 1/10 so với các tấm pin mono

Điện trở của 2 dòng pin mono và poly là gần như nhau, nghĩa là, nồng độ các chất dẫn xuất boron là gần tương đồng. Thông thường, các cell pin mono vẫn thường được biết đến là có mức độ chịu ảnh hưởng bởi hiện tượng BO-LID nhiều hơn so với tấm poly. Và trước khi sản xuất các tấm pin theo công nghệ PERC hàng loạt mà không có quy trình tái hồi phục BO-LID, các tấm pin mono được hiểu rằng là nó sẽ có mức suy hao LID cao hơn so với dòng poly trong năm đầu hoạt động. Chính vì vậy mà các nhà sản xuất thường đảm bảo LID trong năm đầu tiên của tấm mono là 3% trong khi tấm poly là 2.5%. Sự khác biệt này có nguồn gốc chính từ sự suy giảm hiệu suất ban đầu gây ra bởi BO-LID

Cách khắc phục cho hiện tượng BO-LID (Light Induced Regenration – LIR)

Cấu trúc pin theo công nghệ PERC nhạy cảm hơn so với hiện tượng LID do Broton – Oxy (BO-LID). PERC có khả năng hấp thụ ánh sáng hồng ngoại hiệu quả hơn nhờ tích hợp các lớp bổ sung ở phía sau của cell pin để tăng khả năng hấp thụ photon ánh sáng. So với công nghệ BSF truyền thống, hiệu quả của tấm pin PERC tăng lên tuyệt đối khoảng 1%. Tuy nhiên, lượng eletron được tạo ra từ phía sau cells pin của tấm PERC cần phải di chuyển qua khố Si trước khi chúng có thể được phân tách bằng đường giao nhau p-n phía trước một cách hiệu quả. Do vậy mà mặc dù hiệu suất có tăng lên từ lượng electron hấp thụ thụ động từ phía sau pin PERC, nhưng mức suy hao ban đầu do BO-LID lại tăng lên 5% tương ứng.

Đã có nhiều giải pháp được áp dụng để giảm suy hao do BO-LID. Ví dụ như giảm nồng độ boron, tuy nhiên hành động này lại gây giảm đáng kể đến hiệu suất đầu ra của tấm pin, hay như giảm nồng độ oxy trong tế bào pin thì lai tốn khá nhiều chi phí để hình thành phôi pin, v.v. Cho đến năm 2006, quá trình suy hao và hồi phục BO-LID đã được phát hiện bởi Alex Herguth khi tấm pin được thí nghiệm tiếp xúc với ánh sáng ở nhiệt độ cao hoặc nối P-N được phân cực thuận (minh họa như hình 3 dưới đây). Quá trình này có tên gọi là Light Induced Regenration (LIR)

Trong những năm gần đây, công nghệ pin PERC đã và đang được ứng dụng trong sản xuất công nghiệp một cách nhanh chóng, theo đó ứng dụng LIR trong nghiên cứu học thuật để cải thiện hiệu suất pin do suy hao BO-LID cũng được các hãng áp dụng thực tế. Thời gian xử lý LIR đã được rút ngắn đáng kể dưới cường độ ánh sáng mạnh và nhiệt độ cao.

Trong công nghiệp, giải pháp cho BO-LID có thể được sử dụng bằng cách phun dòng điện từ hoặc chiếu tia sáng. Các hình thức chiếu tia sáng bao gồm đèn halogen, LED, Laser hoặc các nguồn khác. Longi là một trong những đơn vị đã sử dụng công nghệ LIR bằng phương pháp chiếu tia laser lên các tấm pin mono – PERC.

Tùy từng phương pháp tiếp cận mà mức độ chiếu tia sẽ khác nhau. Laser là phương pháp cho cường độ mạnh nhất với thời gian của chu trình LIR giảm xuống chỉ còn dưới 5s trong khi những nguồn sáng khác như LED, đèn halogen, v.v thì yếu hơn với chu trình LIR cho những phương pháp này mất khoảng 20-60 giây. Phương pháp phun dòng điện từ có chi phí rẻ hơn nhưng lại đòi hỏi đến 10 phút cho chu trình LIR bởi mức độ phân cực thấp và nhiệt độ không đồng đều so với các phương pháp chiếu sáng.

Hiện tượng LeTID

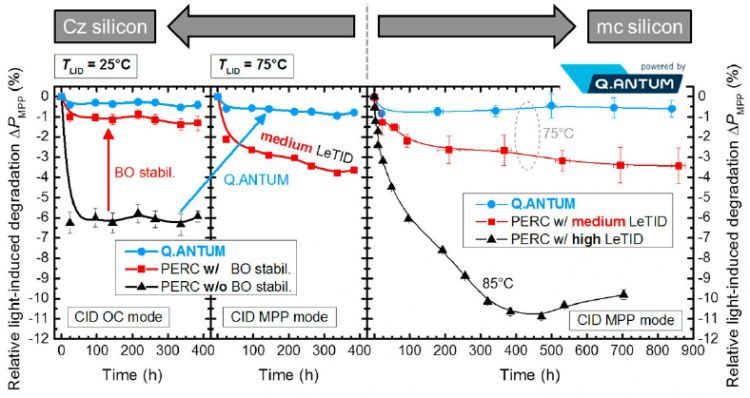

Hiện tượng LeTID khá phổ biến và không chỉ có trong các dòng pin poly đa tinh thể. Theo một nghiên cứu của Fabian Fertig vào năm 2017, mức độ LID của tấm pin mono Cz-Si đạt xấp xỉ khoảng 1-2% trong điều kiện phun dòng điện từ ở 25oC. Trong điều kiện tương đương ở 75oC, hiện tượng suy giảm là như nhau ở cả tấm mono, poly và ở mức trung bình (khoảng 2-4%). Chi tiết được hiển thị như Hình 4:

Loại bỏ suy hao do LeTID

Thực tế, độ suy hao tối đa do hiện tượng LeTID thường xảy ra ở nhiệt độ cao, trong khi các tấm pin thực tế thường vận hành ở nhiệt độ dưới 70oC. Do vậy mà ngoài việc cải thiện về nhiệt độ vận hành tấm pin, sử dụng công nghệ để làm giảm hàm lượng hydro trong chất liệu pin mà các nhà sản xuất cần cải thiện trong thời gian tới thì với những đơn vị lắp đặt, khách hàng có thể hạn chế hiện tượng LeTID bằng cách tránh lắp đặt ở những điểm có nhiệt độ quá nóng và tạo lối thông gió phía dưới giàn pin để làm giảm nhiệt độ trên tấm pin.

Tham khảo thêm các yếu tố khác ảnh hưởng đến hiệu suất tấm pin là PID tại đây