Thế nào là nguy cơ suy giảm hiệu suất (PID) của tấm pin năng lượng mặt trời?

Suy giảm hiệu suất là một tác dụng không mong muốn đối với các tấm năng lượng mặt trời. Thông thường, rất khó để bạn có thể nhận biết được những dấu hiệu rõ ràng ban đầu tuy nhiên nó lại là một trong những nguyên ngân gây ra hiện tượng “chết đột ngột” ở tấm pin. Mặt khác, PID cũng có thể dẫn đến sự hình thành của chuỗi phản ứng dây chuyền tới những tấm pin xung quanh (trong cùng 1 string) với nguy cơ mức suy giảm là gần như nhau, gây ảnh hưởng lớn lên hiệu suất chung của hệ thống.

Vậy hãy cùng Long Tech tìm hiểu xem đâu là nguyên nhân gây nên PID và những biện pháp khắc phục cần được thực hiện để ngăn chặn (hoặc ít nhất là làm giảm) PID, góp phần bảo vệ tấm pin và nâng cao tuổi thọ thực tế của hệ thống

1. Điện áp của hai cực giàn pin so với đất

Một module pin năng lượng mặt trời (dạng đơn hoặc đa tinh thể) thường có điện áp hoạt động ở khoảng 30-40V.

Để tạo ra những dự án điện mặt trời có công suất lớn từ vài trăm kilowatt đến hàng megawat (MW), các tấm năng lượng này cần được ghép nối tiếp để tạo ra điện áp cân bằng từ 200 – 500 V. Tuy nhiên với một số cấu trúc liên kết biến tần thực tế, điện áp được dịch chuyển nhiều hơn về phía cực âm. Do vậy thì để an toàn, toàn bộ các string này sẽ được tiếp nối đất, và chính sự chênh lệch điện áp hai cực của hệ thống so với mặt đất sẽ hình thành nguyên nhân dẫn đến hiện tượng PID. Lấy ví dụ với một hệ thống 400V:

- Nếu Inverter không nối đất và có biến áp cách ly: Điện áp chia đối xứng với +200 ở cực dương và -200 ở cực âm.

- Inverter với biến áp cách ly và cực âm nối đất: Cực âm điện áp bằng 0, điện áp ở cực dương là +400V.

- Inverter với biến áp cách ly và cực dương nối đất: Cực dương điện áp bằng 0, điện áp ở cực âm là -400V.

- Inverter không sử dụng biến áp cách ly (transfomerless): tùy theo thiết kế nhưng thông thường điện áp sẽ được offset về phía âm nhiều hơn. VD: -350V.

Hệ thống năng lượng mặt trời có thể giúp bạn tiết kiệm bao nhiêu?

Công cụ trực tuyến của Long Tech ước tính bạn có thể tiết kiệm từ 50% số tiền điện và sinh lời trong 20 năm theo điều kiện mái nhà và vị trí của bạn.

2. Các hiện tượng PID trên tấm pin

Trong khi hoạt động, khả năng xuất hiện PID ở cực âm của string thường cao hơn. Chênh lệch điện áp cực âm (giả sử -200V) so với khung nhôm tấm pin tạo ra lực điện trường làm cho các ion dương từ tấm kín cường lực (Na+ ) di chuyển vào cell. Các ion Na+ gây ra quá trình ăn mòn điện hoá trên cell dẫn đến suy giảm công suất tấm pin. Đây được gọi là quá trình PID-s.

Ngoài ra, Điện áp cao còn là nguyên nhân dẫn đến các electron di chuyển ra bên ngoài khung tấm pin và đi xuống đất. Đây được gọi là quá trình PID-p. Cả PID-s và PID-p có thể hoặc không thể hồi phục.

Chúng ta có thể quan sát hiện tượng PID trên các module pin màng mỏng như dưới đây, trong đó các phản ứng điện hóa sẽ làm lớp oxit dẫn điện trong suốt (TCO) của các cells pin bị ăn mòn.

3. Các yếu tố ảnh hưởng đến PID

- Chủng loại inverter

Trên thị trường hiện nay phổ biến hai loại inverter là có biến áp ( transfomer ) và không có biến áp (transfomerless) (là dòng inverter phổ biến trên thị trường với giá thành rẻ) . Inverter transformer sử dụng biến áp với chức năng nâng điện áp AC lên bằng với điện áp của lưới. Sử dụng biến áp đồng nghĩa với việc inverter đã được cách ly DC và AC, do đó chúng ta có thể nối cực âm của giàn pin xuống đất. Điều này giúp cực âm của giàn pin có điện áp so với đất bằng 0 và loại bỏ hoàn toàn PID.

- Các thông số của cell và tấm pin

Kính cường lực, lớp EVA, lớp chống phản xạ (ARC) là những yếu tố ảnh hưởng đến PID.

Bản thân kính cường lực với tỉ lệ Natri Cacbonat càng cao sẽ làm tăng PID trong hệ thống.

Lớp EVA (Ethyl Vinyl Acetate) có chứa các loại Axit acetic khi kết hợp với nhiệt độ và độ ẩm cao sẽ làm cho các ion từ tấm kính bám nhiều hơn trên bề mặt cell. Nogài ra, lớp chống phản xạ ARC sử dụng vật liệu chính là Silic nitrua. Tỉ lệ Silic và Nitơ cùng với độ dày của ARC sẽ ảnh hưởng đến PID.

Lớp ARC càng dày sẽ làm cho PID càng phát triển mạnh

- Các thông số môi trường

Độ ẩm và nhiệt độ là hai yếu tố ảnh hưởng đến PID của tấm pin nhiều nhất chúng làm gia tăng dòng rò PID-p.

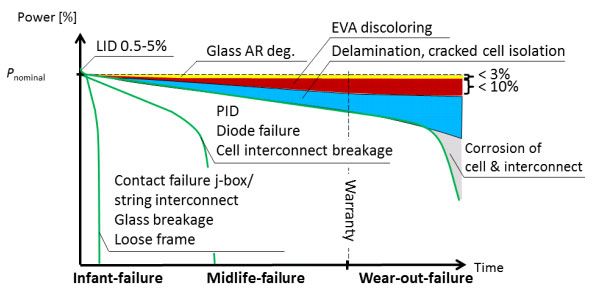

4. PID ảnh hưởng thế nào đến hệ thống

PID là một quá trình phức tạp và có nhiều yếu tố ảnh hưởng. Nhìn chung PID sẽ làm giảm công suất phát và tuổi thọ của tấm pin. PID của tấm pin tăng dần theo thời gian, ảnh hưởng đến Voc và hệ số FF ( Fill Factor ) của tấm pin. Sự suy giàm ảnh hưởng đến tấm pin bị PID và cả string chứa tấm pin. Công suất phát của hệ thống có thể suy giảm lên đến 90% theo thời gian.

5. Các phương pháp làm giảm PID

a. Sử dụng các thiết bị hỗ trợ

Sử dụng inverter trasformer có thể giúp loại bỏ PID của tấm pin khỏi hệ thống. Còn đối với các inverter tansformer less, chúng ta có các thiết bị như PV Off Set box của SMA …

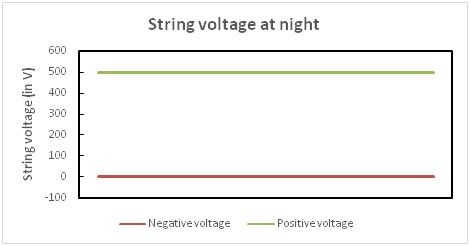

Vào buổi tối, khi điện áp của giàn pin nhỏ hơn giá trị ngưỡng, Offset Box sẽ nâng điện áp của toàn bộ giàn pin lên mức điện áp cao (từ +400V cho đến +1000V so với đất ). Quá trình này giúp đảo ngược sự phân cực xảy ra trên tấm pin vào ban ngày. Đối với hệ thống đã bị PID trong thời gian dài, việc tái tạo lại các tấm pin sẽ mất khoảng 1/2 khoảng thời gian tính từ khi PID xuất hiện. Công suất AC cấp cho bộ Offset Box là rất nhỏ chỉ khoảng 3W.

b. Tấm pin và cell

Chất liệu kính có ít tỉ lệ Natri giúp giảm PID, lớp EVA chúng ta có thể chuyển sang loại vật liệu POE (Poly Olefin Elastomer) giúp giảm PID. tỉ lệ Si:N, độ dày và độ đồng nhất của ARC có thể giúp tấm pin giảm ảnh hưởng của PID

c. Thông số môi trường

Điều tốt nhất là chúng ta nên sử dụng các tấm pin đã đạt tiêu chuẩn IEC để giảm rủi ro do PID gây ra khi hệ thống hoạt động. Các tấm pin đang được test theo tiêu chuẩn IEC TS 62804-1. Quá trình test tấm pin được đặt trong nhiệt độ 80 độ C và độ ẩm trên 85% trong vòng 96 tiếng. Giúp đánh giá ảnh hưởng của các ứng suất lên tấm pin năng lượng mặt trời.

Long Tech phân phối chính thức dòng pin Jinko – thương hiệu đạt chứng nhận IEC TS 62804-1:2015 của IEC về giảm thiểu rủi ro do PID gây ra khi hệ thống hoạt động. Ngoài ra, tấm pin còn được thực hiện thử nghiệm mở rộng trên tiêu chuẩn thử nghiệm được chỉ định để đảm bảo độ tin cậy của sản phẩm trong điều kiện khí hậu khắc nghiệt.

(nguồn: Waaree)